# PCapØ1

Single-chip Solution for Capacitance Measurement with Standard Firmware 03.01.02 April 11th, 2012 Document-No.: DB\_PCapØ1-0301\_e V0.5

## Published by acam-messelectronic gmbh © copyright 2011 by acam-messelectronic gmbh, Stutensee, Germany

#### Legal note

The present manual (data sheet and guide) is still under development, which may result in corrections, modifications or additions. acam cannot be held liable for any of its contents, neither for accuracy, nor for completeness. The compiled information is believed correct, though some errors and omissions are likely. We welcome any notification, which will be integrated in succeeding releases.

The acam recommendations are believed useful, the firmware proposals and the schematics operable, nevertheless it is of the customer's sole responsibility to modify, test and validate them before setting up any production process.

acam products are not designed for use in medical, nuclear, military, aircraft, spacecraft or lifesupport devices. Nor are they suitable for applications where failure may provoke injury to people or heavy material damage. acam declines any liability with respect to such non-intended use, which remains under the customer's sole responsibility and risk. Military, spatial and nuclear use subject to German export regulations.

acam do not warrant, and it is not implied that the information and/or practice presented here is free from patent, copyright or similar protection. All registered names and trademarks are mentioned for reference only and remain the property of their respective owners. The acam logo and the PicoCap logo are registered trademarks of acam-messelectronic gmbh, Germany.

#### Support / Contact

For a complete listing of direct sales contacts, distributors and sales representatives visit the acam website at:

http://www.acam.de

For technical support you can contact the acam support team in the headquarter in Germany or the distributor in your country. The contact details of acam in Germany are:

sales@acam.de or by phone +49 7244 7419 O.

# **Table of Contents**

| 1 System Overview                          |                                                                                                                                                                      | 1-1                             |  |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--|

| 2 Characteristics &<br>Specifications      | 2.1 Electrical Characteristics<br>2.2 CDC Precision                                                                                                                  | 2-2<br>2-3                      |  |

| opecifications                             | <ul><li>2.3 RDC Precision</li><li>2.4 Power Consumption</li><li>2.5 Package Information</li></ul>                                                                    | 2-8<br>2-9<br>2-10              |  |

|                                            | L.J Packaye mormation                                                                                                                                                | 2-10                            |  |

|                                            | 3.1 CDC Measuring Principle<br>3.2 Important CDC Parameters                                                                                                          | 3-2<br>3-2<br>3-4               |  |

| 3 Converter Frontend                       | 3.3 CDC External Circuitry<br>3.4 Connecting the Capacitive                                                                                                          |                                 |  |

|                                            | <ul> <li>3.5 Selecting the Discharge Resist</li> <li>3.6 Compensation Measurement</li> <li>3.7 RDC Temperature Measurement</li> </ul>                                | 3-7                             |  |

| 4 Interfaces (Serial And<br>Pulse-Density) | 4.1 Serial Interfaces<br>4.2 PDM/PWM and GPIO                                                                                                                        | 4-2<br>4-5                      |  |

| 5 Write & Read Registers                   | 5.1 Configuration & Parameter<br>5.2 Explanations to Configuration<br>5.3 Read Registers                                                                             | 5-2<br>5-12<br>5-16             |  |

| 6 DSP, Memory & Firmware                   | <ul> <li>6.1 DSP Management and</li> <li>6.2 Memory Map</li> <li>6.3 Memory Management</li> <li>6.4 OTP Firmware programming</li> <li>6.5 Getting Started</li> </ul> | 6-2<br>6-3<br>6-3<br>6-4<br>6-5 |  |

| 7 Miscellaneous                            | 7.1 Bug Report<br>7.2 Document History                                                                                                                               | 7-2<br>7-3                      |  |

# **1** System Overview

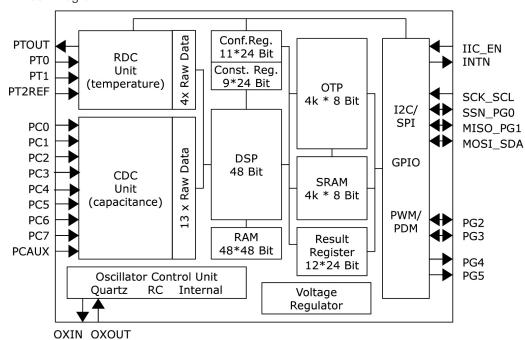

PCapØ1 is a dedicated Capacitance-to-Digital Conversion Digital Signal Processor. Its front end is based on acam's patented **PICO**CAP® principle. This conversion principle offers high resolution at conversion times as short as 2 µs. Customers benefit from outstanding flexibility for optimizing power consumption, resolution and speed.

The PCapO1A can be used for grounded single and differential sensors as well as for floating single and differential sensors. With grounded capacitors the stray capacitance inside the chip will be compensated. With floating capacitors, further to the internal stray capacitance, the external stray capacitances as well get compensated. Additionally, the temperature can be measured by means of internal thermistors or external ones (platinum or others). Before loading some firmware to it, the chip is not completely operable. Data will end up in ALU instead of being transferred to processor and/or output. Under this circumstance, we chose to write a combined data sheet covering the hardware aspects as well as handling a very basic firmware called O3.O1.xx; this basic or "standard" firmware calculates the capacitance and resistance ratios and transfers them to the data output ports, still without doing such further possible processing like filtering and linearization. It is provided free of charge with the chip, yet, it needs to be loaded via SPI or I2C.

For clarity, those aspects that are **standard-firmware related** have been marked with a **blue stripe in the margin**. User-written firmware may behave differently here.

### 1.1 Features

- Digital measuring principle in CMOS technology

- Up to 8 capacitances in grounded mode

- Up to 4 capacitances in floating mode (potential- free and with zero bias voltage)

- Compensation of internal (grounded) and external parasitic capacities (floating)

- High resolution: up to 6 aF at 5 Hz and 10 pF base capacitance, or 17 bit resolution at 5 Hz with 100 pF base capacitance and 10 pF excitation

- High measurement rate: up to 500 kHz

- Extremely low current consumption possible: Down to 4 µA at 3 Hz with 13.4 bit resolution

- High stability with temperature, low offset drift (down to 30 aF per Kelvin), low gain drift when all compensation options are activated.

- Dedicated ports for precision temperature measurement (with Pt1000 sensors, the resolution is 0.005 K)

- Serial interfaces (SPI or I2C compatible)

- Self-boot capability

- Single power supply (2.1 to 3.6 V)

- No need for a clock

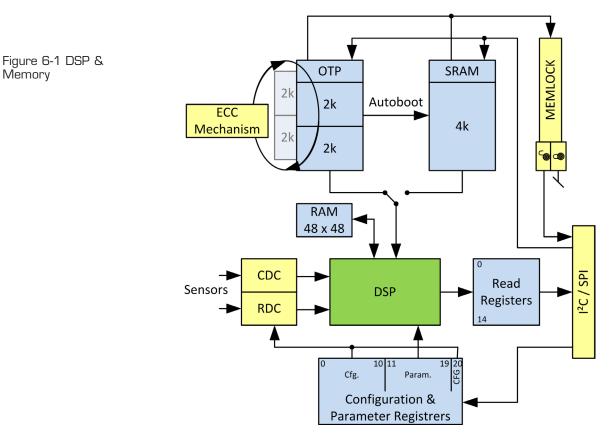

- RISC processor core using Harvard architecture:

- 48 x 48 bit RAM Data

- 4k x 8 bit volatile program memory for high-speed operation (40 to 100 MHz)

- 4k x 8 bit non-volatile (OTP) program memory for normal speed operation (up to 40 MHz)

# 1 System Overview

### 1.2 Applications

- Humidity sensors

- Position sensors

- Pressure sensors

- Force sensors

- Acceleration sensors

- Inclination sensors

### 1.3 Block diagram

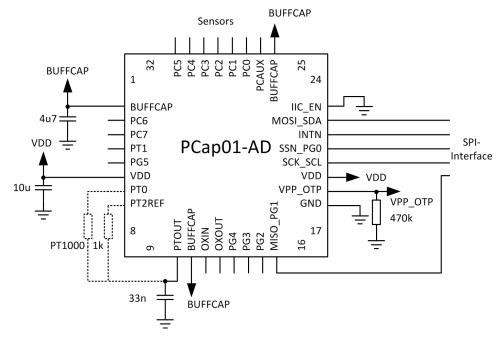

Figure 1-1: Block Diagram

- Tilt sensors

- Angle sensors

- Wireless applications

- Level sensors

- Microphones

- MEMS sensors

### 1.4 Part Numbers

| Ref. | Package | Package Name Conditioning |              |     |

|------|---------|---------------------------|--------------|-----|

| 1613 |         |                           | Waffle Pack  | 100 |

| 1793 |         |                           | Tape-on-reel | 500 |

| 1795 | QFN24   | PCapO1AK                  | Tape-on-reel | 500 |

Sample policy. Single Laboratory samples of packaged chips are available; concerning dice, however, MOQ applies.

| 2 Cha     | aracteristics & Specifications                 | 2-2  |

|-----------|------------------------------------------------|------|

| 2.1 Elect | -<br>trical Characteristics                    | 2-2  |

| 2.1.1     | Absolute Maximum Ratings                       | 2-2  |

| 2.1.2     | Recommended Operating Conditions               |      |

| 2.2 CDC   | Precision                                      | 2-3  |

| 2.2.1     | RMS Noise and Resolution vs. Output Data Rate  | 2-3  |

| 2.2.2     | RMS Noise vs. Supply Voltage                   | 2-6  |

| 2.2.3     | Voltage-Dependent Offset and Gain Error (PSRR) | 2-6  |

| 2.2.4     | Temperature-Dependent Offset and Gain Error    | 2-7  |

| 2.3 RDC   | Precision                                      | 2-8  |

| 2.4 Powe  | er Consumption                                 | 2-9  |

| 2.5 Pack  | age Information                                | 2-10 |

| 2.5.1     | Dice - Pad Layout                              | 2-10 |

| 2.5.2     | QFN Packages                                   | 2-11 |

| 2.5.3     | Pin-Out QFN32 and QFN24 Versions               | 2-11 |

| 2.5.4     | Pin/Pad Assignment                             | 2-12 |

## 2.1 Electrical Characteristics

### 2.1.1 Absolute Maximum Ratings

| Supply voltage V <sub>DD</sub> -to-GND | - 0.3 to 4.0 V                |

|----------------------------------------|-------------------------------|

| Storage temperature Tstg               | - 55 to 150 °C                |

| ESD rating (HBM), each pin             | > 2 kV                        |

| Junction temperature (Tj)              | max. 125 °C                   |

| OTP Data Retention Period              | 10 years at 95 °C temperature |

### 2.1.2 Recommended Operating Conditions

| Quantity               | Symbol                  | Remarks                       | Min.  | Тур.                  | Max.                 | Unit |

|------------------------|-------------------------|-------------------------------|-------|-----------------------|----------------------|------|

| Supply voltage         | V <sub>DD</sub>         |                               | 2.1   |                       | 3.6                  | V    |

| Digital port voltage   | $V_{\text{io_digital}}$ | Relative to ground            | - 0.6 | 3.3                   | V <sub>DD</sub> +0.6 | V    |

|                        | _                       |                               |       |                       | ≤ 3.6                |      |

| Digital ports          |                         | HIGH ‰ LOW                    |       | 0.3 * V <sub>DD</sub> |                      |      |

| switching level        |                         | LOW % HIGH                    |       | 0.7 * V <sub>DD</sub> |                      |      |

| Analog port voltage    | $V_{io\_analog}$        |                               | - 0.6 |                       | V <sub>DD</sub> +0.6 | V    |

|                        | _ 0                     |                               |       |                       | ≤ 3.6                |      |

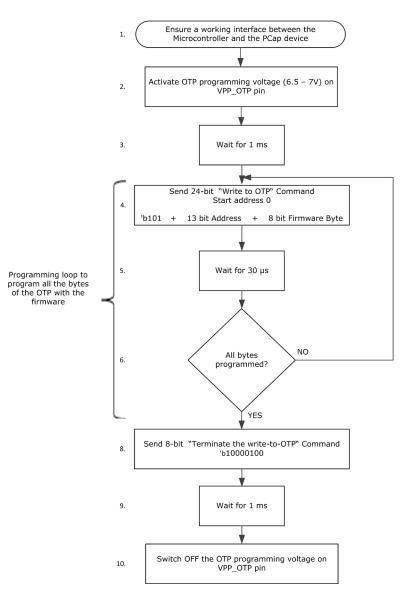

| OTP Programming        | V <sub>OTP</sub>        | Between "VPP_OTP" port        |       | 6.5                   | 7.0                  | V    |

| voltage                |                         | and ground.                   |       |                       |                      |      |

| SPI bus frequency      | f <sub>SPI-bus</sub>    | Clock frequency for the       | 0     |                       | 20                   | MHz  |

|                        |                         | 4-wire SPI bus operation      |       |                       |                      |      |

| Buffer strength        |                         | e.g. for the MISO line        |       |                       | 2.5                  | mA   |

| I2C bus frequency      |                         | Speed (data rate) of the      | 0     | 100                   |                      | kHz  |

|                        |                         | 2-wire I2C bus operation      |       |                       |                      |      |

| OTP Bit hold time      |                         | Bit hold time for OTP write   | 30    |                       | 500                  | μs   |

| GPIO input rise time   |                         | Rise time of the input signal |       |                       | t.b.d                | ns   |

|                        |                         | put to general-purpose I/O    |       |                       |                      |      |

| GPIO output rise time  |                         | Rise time of the output sig-  |       |                       | t.b.d.               | ns   |

|                        |                         | nal from a general-purpose    |       |                       |                      |      |

|                        |                         | 1/0                           |       |                       |                      |      |

| CDC discharge time     |                         | MR1                           | 0     |                       | 40                   | μs   |

| RDC discharge time     |                         |                               | 0     |                       | 100                  | μs   |

| Junction Temperature T |                         | Junction temperature must     | - 40  |                       | + 125                | °C   |

|                        | 1                       | not exceed +125 °C            |       |                       |                      |      |

| Ambient Temperature    | T                       | At VDD = 2.4V -/+ 0.3V        | - 40  |                       | + 125                | °C   |

Table 2-1: Operating conditions

Overclocking the I2C bus is technically possible but within the sole responsibility of the customer (a license may be necessary).

### 2.2 CDC Precision

### 2.2.1 RMS Noise and Resolution vs. Output Data Rate

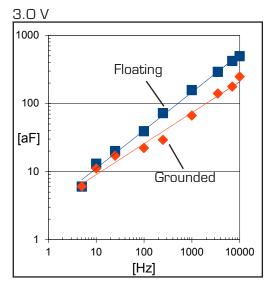

Table 2-2 Typical Capacitive Noise & Resolution vs. Output Data Rate, 10 pF Base + 1 pF Span, fast settle, V = 3.0 V

| Output | FLOATING                 |              |                | GROUNDED     |                       |                |  |  |

|--------|--------------------------|--------------|----------------|--------------|-----------------------|----------------|--|--|

| Data   | Fully comp               | pensated     |                | Internally c | nternally compensated |                |  |  |

| Rate   | RMS                      | Eff. Resolu- | Eff. Resoluti- | RMS          | Eff. Resolu-          | Eff. Resoluti- |  |  |

| [Hz]   | Noise                    | tion 10 pF   | on 1 pF span   | Noise        | tion 10 pF            | on 1 pF span   |  |  |

|        | [aF]                     | base [Bits]  | [Bits]         | [aF]         | base [Bits]           | [Bits]         |  |  |

| 5      | 6                        | 20.7         | 17.3           | 6            | 20.7                  | 17.3           |  |  |

| 10     | 13                       | 19.6         | 16.2           | 11           | 19.8                  | 16.5           |  |  |

| 25     | 20                       | 18.9         | 15.6           | 17           | 19.2                  | 15.8           |  |  |

| 100    | 39                       | 18.0         | 14.6           | 22           | 18.8                  | 15.5           |  |  |

| 250    | 72                       | 17.1         | 13.8           | 29           | 18.4                  | 15.1           |  |  |

| 1,000  | 157                      | 16.0         | 12.6           | 66           | 17.2                  | 13.9           |  |  |

| 3,500  | 3,50029015.17,00042014.5 |              | 11.8           | 139          | 16.1                  | 12.8           |  |  |

| 7,000  |                          |              | 11.2           | 176          | 15.8                  | 12.5           |  |  |

| 10,000 | 495                      | 14.3         | 11.0           | 246          | 15.3                  | 12.0           |  |  |

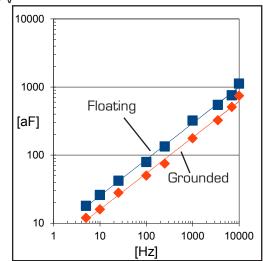

Root mean-square (RMS) noise in aF as a function of output data rate in Hz, measured at 3.0 V supply voltage using the maximum possible sample size for in-chip averaging at the minimum possible cycle time. Bit values are calculated as a binary logarithm of noise (in attofarad) over the base and excitation capacitance values. The measurements have been done with the PCapO1 evaluation board, with fixed COG ceramic capacitors.

Both, sensor and reference are connected "floating" or "grounded", as indicated. When floating, compensation mechanisms for both internal and external stray capacitance are activated; when grounded, internal only.

Table 2-3 Typical Capacitive Noise & Resolution vs. Output Data Rate, 33 pF Base + 3.3 pF Span, fast settle, V = 3.0 V

| Output | FLOATING   |              |              | GROUNDED     |                        |              |  |  |

|--------|------------|--------------|--------------|--------------|------------------------|--------------|--|--|

| Data   | Fully comp | pensated     |              | Internally c | Internally compensated |              |  |  |

| Rate   | RMS        | Eff. Resolu- | Eff. Resolu- | RMS          | Eff. Resolu-           | Eff. Resolu- |  |  |

| [Hz]   | Noise      | tion 33 pF   | tion 3.3 pF  | Noise        | tion 33 pF             | tion 3.3 pF  |  |  |

|        | [aF]       | base [Bits]  | span [Bits]  | [aF]         | base [Bits]            | span [Bits]  |  |  |

| 5      | 18         | 20.8         | 17.5         | 12           | 21.4                   | 18.1         |  |  |

| 10     | 10 26 20.3 |              | 17.0         | 16           | 21.0                   | 17.7         |  |  |

| 25     | 42         | 19.6         | 16.3         | 28           | 20.2                   | 16.8         |  |  |

| 100    | 79         | 18.7         | 15.4         | 50           | 19.3                   | 16.0         |  |  |

| 250    | 134        | 17.9         | 14.6         | 75           | 18.7                   | 15.4         |  |  |

| 1,000  | 321        | 16.6         | 13.3         | 176          | 17.5                   | 14.2         |  |  |

| 3,500  |            |              | 12.6         | 325          | 16.6                   | 13.3         |  |  |

| 7,000  |            |              | 12.1         | 508          | 16.0                   | 12.7         |  |  |

| 10,000 | 1119       | 14.8         | 11.5         | 742          | 15.4                   | 12.1         |  |  |

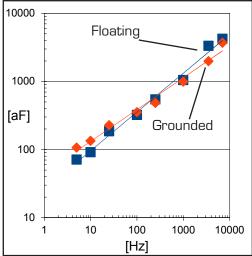

Table 2-4 Typical Capacitive Noise & Resolution vs. Output Data Rate, 100 pF Base + 10 pF Span, fast settle, V = 3.0 V

| Output | FLOATING   |              |              | GROUNDED     |                       |              |  |  |

|--------|------------|--------------|--------------|--------------|-----------------------|--------------|--|--|

| Data   | Fully comp | pensated     |              | Internally c | nternally compensated |              |  |  |

| Rate   | RMS        | Eff. Resolu- | Eff. Resolu- | RMS          | Eff. Resolu-          | Eff. Resolu- |  |  |

| [Hz]   | Noise      | tion 100 pF  | tion 10 pF   | Noise        | tion 100 pF           | tion 10pF    |  |  |

|        | [aF]       | base [Bits]  | span [Bits]  | [aF]         | base [Bits]           | span [Bits]  |  |  |

| 5      | 71         | 20.4         | 17.1         | 106          | 19.8                  | 16.5         |  |  |

| 10     | 91         | 20.1         | 16.7         | 133          | 19.5                  | 16.2         |  |  |

| 25     | 185        | 19.0         | 15.7         | 226          | 18.8                  | 15.4         |  |  |

| 100    | 321        | 18.2         | 14.9         | 350          | 18.1                  | 14.8         |  |  |

| 250    | 543        | 17.5         | 14.2         | 480          | 17.7                  | 14.3         |  |  |

| 1,000  | 1044       | 16.5         | 13.2         | 987          | 16.6                  | 13.3         |  |  |

| 3,500  | 3320       | 14.9         | 11.6         | 1965         | 15.6                  | 12.3         |  |  |

| 7,000  | 4226       | 14.5         | 11.2         | 3675         | 14.7                  | 11.4         |  |  |

# 2 Characteristics & Specifications

Figure 2-1 Typical Capacitive Noise vs. Output Data Rate, with 10 pF Base Capacitance, V =

Figure 2-3 Typical Capacitive Noise vs. Output Data Rate, with 100 pF Base Capacitance, V = 3.0 V

Figure 2-2 Typical Capacitive Noise vs. Output Data Rate, with 33 pF Base Capacitance, V = 3.0 V

# 2 Characteristics & Specifications

## 2.2.2 RMS Noise vs. Supply Voltage

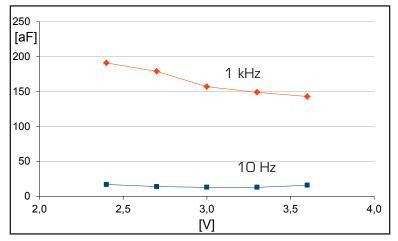

Figure 2-4 RMS Noise vs. Supply Voltage

RMS Noise expressed in aF as a function of VDD power supply voltage.

The upper curve is for 1 kHz output data rate, the lower curve for 10 Hz.

Data acquired like before with 10 pF ceramic COG capacitors connected "floating" in place of reference and sensor. The excitation capacitor was a 1 pF ceramics COG type.

## 2.2.3 Voltage-Dependent Offset and Gain Error (PSRR)

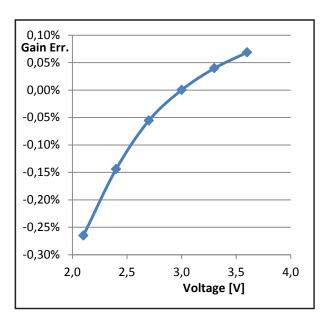

Figure 2-5 Gain Error in % vs. Supply Voltage (Power Supply Rejection Ratio)

Data acquired like before with 100 pF ceramic COG capacitors connected "floating" in place of reference and sensor. The excitation capacitor was a 10 pF ceramics COG type.

The gain drift is the principal contribution to the error; offset drift is negligible. No dependency on update rate has been detected.

At present, power-supply rejection ratio is poor, so the component needs well-filtered, stable supply voltages. Linear regulators will be indicated in most cases. The data presented here have been acquired in such conditions.

Any switching regulator in the supply line must be separated from the chip through a linear voltage regulator, combined with some purposefully designed RC filter. Any drift and noise in the supply line add error and noise to the output.

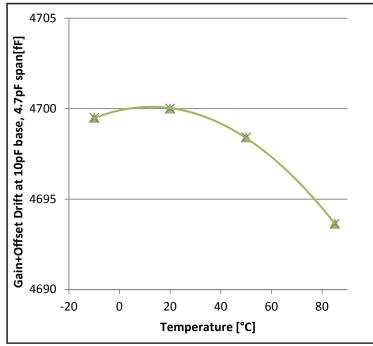

### 2.2.4 Temperature-Dependent Offset and Gain Error

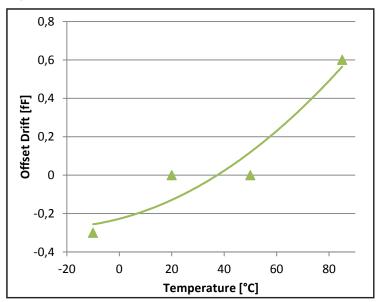

Figure 2-6 Offset Drift vs. Temperature

Offset drift as a function of temperature at 3.OV supply voltage VDD. 10 pF base capacitance, both sensor and reference, a COG ceramics capacitor each, connected "floating".

Offset Drift:

3.0 V: 9.5 aF/K

Gain drift as a function of temperature at 3.0V supply voltage VDD. 10 pF base capacitance, both sensor and reference, plus 4.7 pF span, with COG ceramics capacitors each, connected "floating".

Offset Drift:

3.0 V: 13 ppm/K

# 2 Characteristics & Specifications

## 2.3 RDC Precision

Thermoresistive Coefficients Tk at 20 °C

| Material                       | Tk         |  |  |

|--------------------------------|------------|--|--|

| Internal polysilicon reference | -1.1ppm/K  |  |  |

| Internal aluminum thermistor   | 2830 ppm/K |  |  |

| External PT1000 sensor         | 3830 ppm/K |  |  |

Resolution with internal Al/PolySi at 20 °C

| Measurement Conditions                 | R2/Rref typ. | RMS noise | Typical RMS noise |

|----------------------------------------|--------------|-----------|-------------------|

|                                        |              | R2/Rref   | Temperature(*)    |

| No averaging, 2 fake measurements      | 0.825        | 50 ppm    | 25 mK             |

| 16-fold averaging, 8 fake measurements | 0.823        | 10 ppm    | 5 mK              |

(\*) after linearization in post-processing software

Typical Error with internal Al-thermometer after linearization and conversion into temperature, assuming a linear relation between temperature and resistivity:

-20 °C < Temp. < 0 °C 290 mK

0 °C < Temp. < 80 °C 110 mK

## 2.4 Power Consumption

Table 2-5 Total Current I [ $\mu$ A] as a function of speed (SEQTIME) and resolution (C\_AVRG) in Triggered Mode

| 5   | EQTIME       |        | Ι [μΑ]                         |        |        |        |        |        |        |        |  |

|-----|--------------|--------|--------------------------------|--------|--------|--------|--------|--------|--------|--------|--|

| dat | a rate [Hz]) |        | C_AVRG (RMS resolution [Bits]) |        |        |        |        |        |        |        |  |

|     |              | 1      | 4                              | 16     | 64     | 128    | 256    | 512    | 1024   | 2048   |  |

|     |              | (11.3) | (12.3)                         | (13.4) | (14.4) | (14.9) | (15.4) | (15.9) | (16.4) | (16.9) |  |

| 13  | (3.1)        | 4      | 4                              | 4      | 5      | 10     | 10     | 55     | 80     | 150    |  |

| 12  | (6.1)        | 4      | 5                              | 7      | 10     | 20     | 35     | 80     | 150    |        |  |

| 11  | (12.2)       | 5      | 6                              | 9      | 22     | 40     | 80     | 160    |        |        |  |

| 10  | (24.4)       | 6      | 8                              | 15     | 44     | 82     | 160    |        |        |        |  |

| 9   | (48.8)       | 8      | 12                             | 27     | 85     | 160    |        |        |        |        |  |

| 8   | (97.7)       | 12     | 20                             | 49     | 163    |        |        |        |        |        |  |

| 7   | (195.0)      | 20     | 35                             | 93     |        |        |        |        |        |        |  |

| 6   | (391.0)      | 36     | 65                             | 178    |        |        |        |        |        |        |  |

| 5   | (781.0)      | 67     | 124                            |        |        |        |        |        |        |        |  |

| 4   | (1560.0)     | 127    | 236                            |        |        |        |        |        |        |        |  |

| 3   | (3120.0)     | 229    |                                |        |        |        |        |        |        |        |  |

| 2   | (6250.0)     | 409    |                                |        |        |        |        |        |        |        |  |

Table 2-6 Total Current I [ $\mu$ A] as a function of speed (SEQTIME) and resolution (C\_AVRG) in Continuous Mode (this mode yields highest possible speed/performance)

| =      |        | 0 1                            |        |        |        | -      |        |        |        |

|--------|--------|--------------------------------|--------|--------|--------|--------|--------|--------|--------|

|        |        | C_AVRG (RMS resolution [Bits]) |        |        |        |        |        |        |        |

|        | 1      | 4                              | 16     | 64     | 128    | 256    | 512    | 1024   | 2048   |

|        | (11.3) | (12.3)                         | (13.4) | (14.4) | (14.9) | (15.4) | (15.9) | (16.4) | (16.9) |

| Ι [μΑ] | 515    | 275                            | 204    | 185    | 182    | 181    | 180    | 180    | 179    |

Temperature measurement in addition to capacitive measurement will add between 2 and 10  $\mu$ A approximately, depending on speed. Total consumption values below 30  $\mu$ A may be obtained only when driving the on-chip 1.8 volts core supply generator in an energy-saving mode (see section 5, register 10); ultimate microamp savings with DSP slowed down (see section 5, register 8).

## 2.5 Package Information

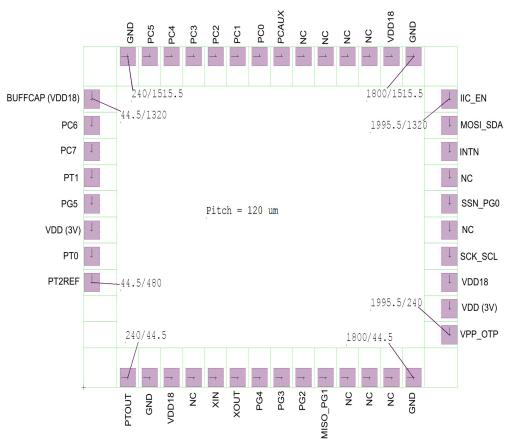

## 2.5.1 Dice - Pad Layout

Die dimensions: 2.15 mm x 1.67 mm with pad pitch 120  $\mu m$ , pad opening is 85  $\mu m$  x 85  $\mu m$

Die thickness: 380 µm

Figure 2-8: Pad Layout

# 2 Characteristics & Specifications

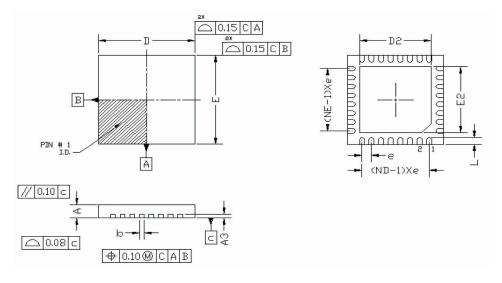

## 2.5.2 QFN Packages

Figure 2-9: QFN package dimensions

Table 2-7: QFN Dimensions

|             |         | Dimension | Dimensions in mm |   |     |      |      |          |      |  |  |

|-------------|---------|-----------|------------------|---|-----|------|------|----------|------|--|--|

| Device Name | Package | D, E      | D2, E2           | N | е   | L    | b    | А        | A3   |  |  |

| PCapO1-AD   | QFN32   | 5.00      | 3.70             | 8 | 0.5 | 0.4  | 0.25 | 0.75/0.9 | 0.20 |  |  |

| PCapO1-AK   | QFN24   | 4.00      | 2.70             | 6 | 0.5 | 0.35 | 0.25 | 0.75/0.9 | 0.20 |  |  |

Dimensioning and tolerances acc. to ASME Y14.5M-1994

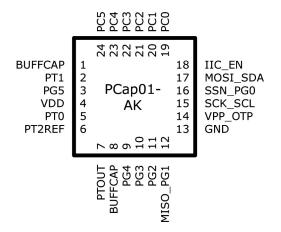

# 2.5.3 Pin-Out QFN32 and QFN24 Versions

PC5 PC4 PC3 PC3 PC3 PC1 PC1 PC0 BUFFCAP BUFFCAP 24 IIC\_EN 1 2 3 MOSI\_SDA PC6 23 PC7 22 INTN PT1 4 5 6 7 PCap01-AD 21 SSN\_PG0 PG5 20 SCK\_SCL VDD 19 VDD PT0 18 VPP OTP PT2REF GND 8 17 9 111 112 113 113 115 115 OXIN OXOUT PG4 PG3 PG3 PG2 MIS0\_PG1 PTOUT BUFFCAP

-AD: All pins are available

Figure 2-11

-AK: Reduced number of capacitor ports, no external oscillator

### 2.5.4 Pin/Pad Assignment

| Pin      | Description                                                                                                    | Com-                     | Pin N | lum- |

|----------|----------------------------------------------------------------------------------------------------------------|--------------------------|-------|------|

|          |                                                                                                                | ment                     | ber   |      |

|          |                                                                                                                |                          | -AD   | -AK  |

| BUFFCAP  | Connect microfarad bypass capacitance and nanofarad bypass                                                     | 1                        | 1     | 1    |

|          | capacitance to GND. Bridge all BUFFCAP pins. Bypassing is mandatory!                                           | connec-<br>ase           | 10    |      |

|          |                                                                                                                | e con<br>case            | 25    | 8    |

| GND      | Ground                                                                                                         | jā >                     | 17    | 13   |

| IIC_EN   | Put this to LOW or GND for use of SPI bus. Put it to HIGH or VDD otherwise.                                    | Need to be<br>ted in any | 24    | 18   |

| INTN     | Optional. Interrupt line, low active                                                                           |                          | 22    |      |

| MISO_PG1 | Serial interface data line, Master In - Slave Out (SPI only, other-<br>wise available as general-purpose port) | unconnec<br>lot used     | 16    | 12   |

| MOSI_SDA | Serial interface data line, Master Out - Slave In                                                              | not nu                   | 23    | 17   |

| OXIN     | May be left open. Very exceptionally used for connecting a 4 to                                                | ≓. ≷                     | 11    |      |

| OXOUT    | 20 MHz ceramics resonator or quartz.                                                                           | Lea<br>ted               | 12    |      |

| Pin               | Description                                                                                                                                                                                                         | Com-                          | Pin N | lum- |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------|------|

|                   |                                                                                                                                                                                                                     | ment                          | ber   |      |

|                   |                                                                                                                                                                                                                     |                               | -AD   | -AK  |

| PCO               | "CDC" or capacitive measurement ports. Connect reference                                                                                                                                                            |                               | 27    | 19   |

| PC1               | and sensors here, beginning with PCØ for the reference.                                                                                                                                                             |                               | 28    | 20   |

| PC2               |                                                                                                                                                                                                                     |                               | 29    | 21   |

| PC3               |                                                                                                                                                                                                                     |                               | 30    | 22   |

| PC4               |                                                                                                                                                                                                                     |                               | 31    | 23   |

| PC5               |                                                                                                                                                                                                                     |                               | 32    | 24   |

| PC6               |                                                                                                                                                                                                                     |                               | 2     |      |

| PC7               |                                                                                                                                                                                                                     |                               | З     |      |

| PCAUX             | May be used for external discharge resistor.                                                                                                                                                                        | sed                           | 26    |      |

| PG2               | General purpose I/O ports. PG4 and PG5 are output only,                                                                                                                                                             | t n                           | 15    | 11   |

| PG3               | others are configurable input or output.                                                                                                                                                                            | it no                         | 14    | 10   |

| PG4               |                                                                                                                                                                                                                     | ba                            | 13    | 9    |

| PG5               |                                                                                                                                                                                                                     | lect                          | 5     | 3    |

| PTO               | "RDC" or temperature measurement ports. Connect one side                                                                                                                                                            |                               | 7     | 5    |

| PT1               | of the external resistive sensors here.                                                                                                                                                                             | Dun                           | 4     | 2    |

| PT2REF            | When there is an external resistive (temperature measure-<br>ment) reference, connect it here, otherwise this is the place<br>for a third resistive sensor.                                                         | Leave unconnected if not used | 8     | 6    |

| PTOUT             | For temperature measurement, connect the other side of the resistive sensors and a 33 nF ceramics capacitor here.                                                                                                   | ]                             | 9     | 7    |

| SCK_SCL           | Serial interface clock line                                                                                                                                                                                         |                               | 20    | 15   |

| SSN_PGO           | SPI interface chip select line, low active.                                                                                                                                                                         | ]                             | 21    | 16   |

|                   | Alternatively general purpose I/O port.                                                                                                                                                                             |                               |       |      |

| VDD               | VDD here, plus bypass capacitance to GND. Bypassing is man-                                                                                                                                                         | 1                             | 6     | 4    |

|                   | datory!                                                                                                                                                                                                             |                               | 19    |      |

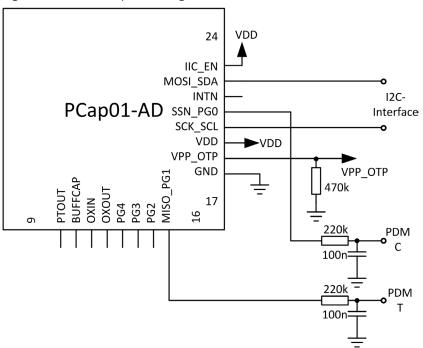

| VPP_OTP           | Set to 6.5 V during OTP programming. Set back to GND rapid-<br>ly after the end of the programming process. Keep pin groun-<br>ded for normal device operation. Apply a 470 kOhm pull-down<br>resistor to this pin. | Connect<br>to GND             | 18    | 14   |

| GND ground<br>pad | The ground pad, bottom located, is internally connected to ground. Parallel external grounding is not necessary                                                                                                     |                               | -     | -    |

| 3   | Converter Frontend                | 3-2  |

|-----|-----------------------------------|------|

|     | CDC Measuring Principle           |      |

| 3.2 | Important CDC Parameters          | .3-2 |

| 3.3 | CDC External Circuitry            | .3-4 |

| 3.4 | Connecting the Capacitive Sensors | .3-5 |

| 3.5 | Selecting the Discharge Resistor  | .3-6 |

| 3.6 | Compensation Measurement          | .3-7 |

| 3.7 | RDC Temperature Measurement       | .3-8 |

## 3.1 CDC Measuring Principle

The device uses "discharge time measurement" as a principle for measuring either capacitance (the <u>CDC</u> unit) or resistivity (the <u>RDC</u> unit). It addresses all ports (PC...,PT...) in time multiplex.

### 3.2 Important CDC Parameters

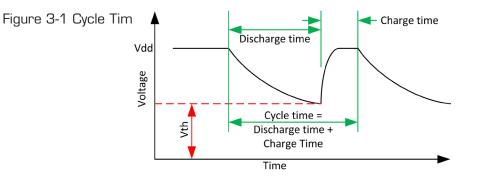

An important notion is "cycle time", the period of one elementary discharge-and-recharge cycle, see figure 3-1.

The discharge time is given by the capacitors and the discharge resistor. The cycle time is the time interval between two discharge time measurements and is set by the user. The relevant parameter is CMEAS\_CYTIME in register 4. The user has to take care that the charge time and therefore the cycle time is long enough. As default we recommend to have the cycle time > 2 x discharge time. Otherwise, the capacitors do not get charged sufficiently. Further, if the cycle time is less than the discharge time the CDC will show a time-out.

Measurement results are deduced as follows; discharge time ratios equal sensor-to-reference values:  $\frac{\tau_N}{c_N} = \frac{C_N}{c_N}$

$$\frac{\tau_N}{\tau_{ref}} = \frac{C_N}{C_{ref}}$$

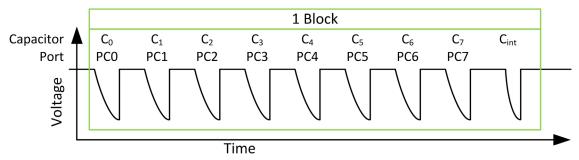

This equation holds for the CDC, and is similar for the RDC. Figure 3-2 Charging-/ discharging cycles grounded, compensated, single or differential sensors

Figure 3-2 shows a CDC example with 7 single / 3 differential grounded sensors plus one reference. One measurement block is made of a discharge time measurement for each capacitor and an ad-

ditional one for measuring the internal stray capacitances and comparator delay (internal compensation). Figures 3-2 and 3-3 have symbolic meaning only, explaining the principle. No realistic scope shots.

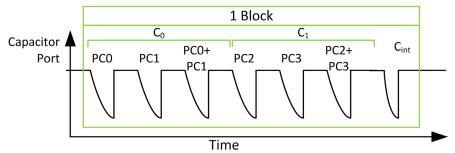

Figure 3-3 Charging-/ discharging cycles floating, compensated, single and differential sensors

Figure 3-3 shows a CDC example with one floating single sensor plus reference / one floating differential sensor. One measurement block is made of 3 discharge time measurements for each capacitor, including the external compensation measurement, and an additional one for measuring the internal stray capacitances and comparator delay. See section 3.6 for further details on the compensation.

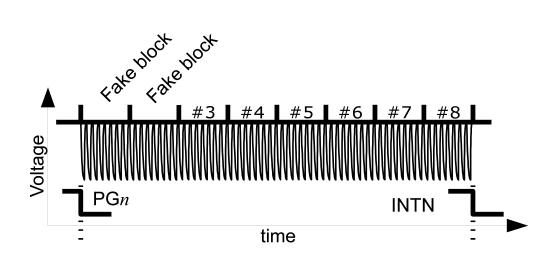

Measurement rate or "output data rate" is inversely proportional to the cycle time and to the sum of "fake block number" and "averaging sample size". If neither fake blocks nor on-chip averaging are requested, results will be updated after every "block".

Figure 3-4 Measurement cycle

| Example 1:                                                      |                                |

|-----------------------------------------------------------------|--------------------------------|

| 2 single grounded sensors + reference, cycle time = 20 $\mu$ s: | block period = 80 µs           |

| 2 fake blocks + 4-fold averaging:                               | measurement period = 480 µs    |

|                                                                 | Maximum update rate = 2,083 Hz |

| Example 2:                                                      |                                |

| 1 single floating sensor + reference, cycle time = 20 $\mu$ s:  | block period = 140 µs          |

| 2 fake blocks + 8-fold averaging:                               | measurement period = 1400 µs   |

|                                                                 | Maximum update rate = 714 Hz   |

|                                                                 |                                |

### 3.3 CDC External Circuitry

Figure 3-5 shows the part of the schematic that is independent from capacitive sensor configuration. Here an example with the SPI interface used.

Figure 3-5: Schematics with sensors not shown<sup>1</sup>

1 Remark: Bypass capacitors should be ceramics type. Low noise operation is conditioned by a good bypassing. Place bypass close to the pins.

## **3 Converter Frontend**

### 3.4 Connecting the Capacitive Sensors

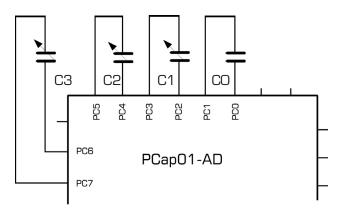

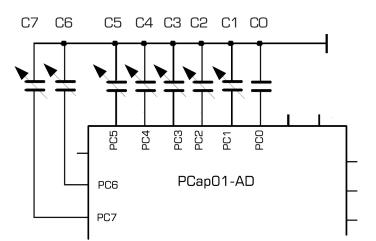

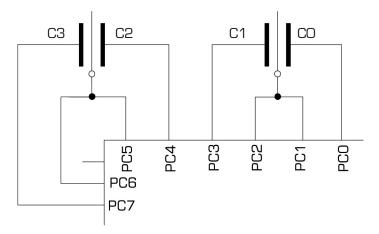

The capacitive-sensor part of the schematic:

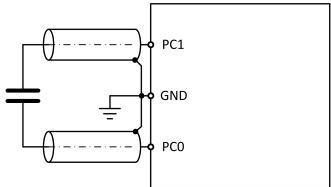

Figure 3-6: Single sensors, floating, up to 3 sensors (C1 to C3) and one reference (CO)

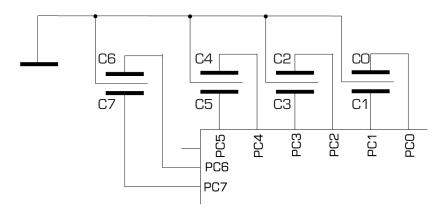

Figure 3-7: Single sensors, grounded, up to 7 sensors and one reference

Figure 3-8: Differential sensors, floating

# **3** Converter Frontend

Figure 3-9: Differential sensors, grounded.

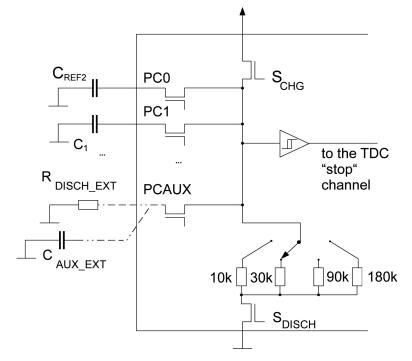

### 3.5 Selecting the Discharge Resistor

The measurement is based on controlled discharging; within the CDC part, four selectable discharge resistivities down to 10 kOhms in size are available (see figure 3-10). They are useful for base capacitances from zero up to approx. 3.5 nF. Not described in this short manual is the possibility of extending the measuring range to even higher capacitance values by connecting a small resistivity outside the chip.

Figure 3-10: CDC Dimensioning

### 3.6 Compensation Measurement

With grounded capacitors the PCapO1 offers the possibility to compensate for internal parasitic capacitances and, having the same effect, the propagation delay of the comparator. ACAM patents pending.

With floating capacitors we have the additional option to compensate external parasitic capacitances against ground. On the PCB, the wire capacitance typically refers to ground. For long wires, it is recommended to use shields which should be grounded at their PCB side.

Figure 3-11 shows how shielded cables should be connected for compensation of the external parasitic capacitances.

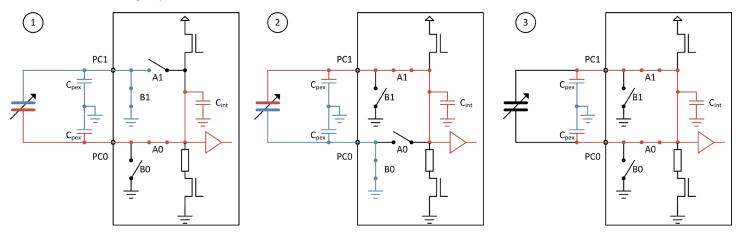

Three measurements are necessary for each capacitor in case of floating sensors; this is shown in figure 3-12

Figure 3-12 Floating capacitors, external compensation measurements, the three measurements that are made for each floating capacitor.

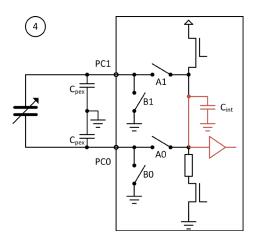

For the internal compensation measurement, both switches A1 and AO are open. Only the internal parasitic capacitance and the comparator propagation delay will thus be measured.

Figure 3-13 Grounded/floating capacitors, internal compensation measurement

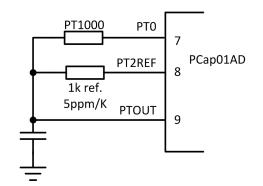

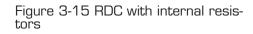

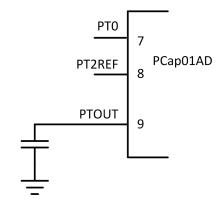

### 3.7 **RDC** Temperature Measurement

The chip device has two on-chip resistor elements for the measurement of temperature, an aluminum strip with TK  $\approx$  2800 ppm/K as a sensor and a polysilicon resistor with TK "close to zero" as a reference.

As an alternative, it is possible to connect the temperature sensor and reference resistor externally. (In general the chip may support two external sensors, but this option is not supported by O3.O1 firmware).

In any case, it is mandatory to connect an external 33 nF capacitor, because the the temperature measurement, too, is discharge time based. For the capacitor, COG ceramics yields best performance, whilst X7R material yields fair results.

In principle, external and internal thermometers/reference may be mixed, e.g. an external PT1000 may be compared to the internal Poly-Si resistor.

The selection between internal and external resistors is done by TMEAS\_7BITS in register 6:

External solution

Firmware Related

3

A)

Configuration:

Output data: Ratio PT1000/Rref as R0/Rref in read register Res10 (address 13).

Register 5 = 'h CX XX XX

- B) Completely internal solution

- Configuration:

- Register 4 = 'h XX XX O1 (CMEAS triggered)

Register 4 = 'h XX XX O1 (CMEAS triggered)

Register 6 = 'h 00 0C 40 (external resistors)

- Register 5 = 'h CX XX XX

- Register 6 = 'h 00 43 40 (external resistors)

- Output data:

- Ratio R[AI]/R[Si\_poly] as R2/Rref in read register Res11 (address 14).

**Converter Frontend**

Figure 3-14 RDC with external resistors

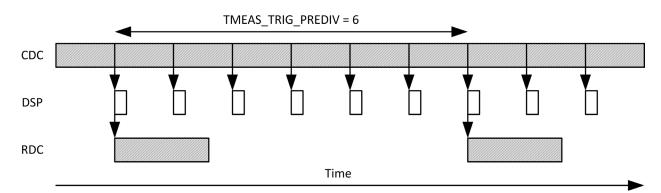

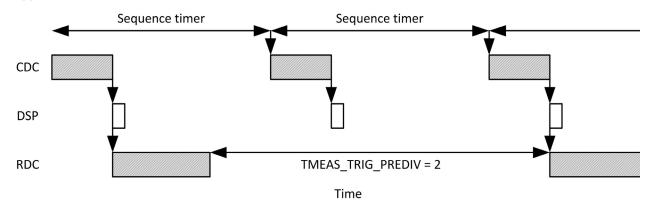

There are various trigger sources for the temperature measurement, set in register 4 by parameter TMEAS\_TRIG\_SEL. We strongly recommend to use TMEAS\_TRIG\_SEL = 1, trigger by capacitance measurement. With this setting, the temperature measurement follows directly each Nth capacitance measurement, where N is set by parameter TMEAS\_TRIG\_PREDIV in register 5. With TMEAS\_TRIG\_PREDIV = 0 the temperature measurement is done with each capacitance measurement. With TMEAS\_TRIG\_SEL = 0 the temperature measurement is triggered by software, sending opcode 'h8E. If no opcode is sent the temperature measurement is switched off.

For low power applications, it is recommended to set the divider TMEAS\_TRIG\_PREDIV to such a value that the temperature measurement is done maximum 10 times per second.

## **3 Converter Frontend**

Figure 3-16 Temperature Measurement triggered by Capacitance Measurement (continuous mode)

Figure 3-17 Temperature Measurement triggered by Capacitance Measurement (Sequence timer triggered)

Be aware that the resistivity measurement is based on an AC, not a DC, method. So, cable between sensor and chip may contribute shift and noise through its inductance and capacitance. Twisted shielded cable may be a good choice, in some cases an active shield may help.

Issue a start command (op code 0x8C) and begin polling data or watching INTN. See sections 5.3, 6.5.3 and 6.5.4 for details. What you read is RO/Rref or R2/Rref, a ratio between two resistivities.

External or internal sensors — you will need to calibrate either solution in a climate chamber.

| 4 Int   | erfaces (Serial And Pulse-Density)    |     |

|---------|---------------------------------------|-----|

|         | al Interfaces                         |     |

| 4.1.1   | Op codes                              | 4-2 |

| 4.1.2   | I <sup>2</sup> C Compatible Interface | 4-3 |

| 4.1.3   | The 4-wire, SPI interface             | 4-4 |

| 4.2 PDN | ///PWM and GPIO                       | 4-5 |

# 4 Interfaces (Serial And Pulse-Density)

### 4.1 Serial Interfaces

For operation with a micro-controller, and also for programming the device, two serial interfaces are available. Only one interface is available at a time, selected through the voltage applied to the pin "IIC\_EN". Both interfaces are limited to "slave" rank, and both permit programming :

| Pin IIC_EN is connected to GROUND | The 4-wire SPI interface is active. General-purpose I/O    |

|-----------------------------------|------------------------------------------------------------|

|                                   | pins PGO and PG1 are not available (occupied by SPI).      |

| Pin IIC_EN is connected to VDD    | The 2-wire I2C interface is active and all general-purpose |

|                                   | I/O pins are available, including PGO and PG1.             |

Remarks: The general-purpose I/O pins PG2 through PG5 are available in either case. If no controller interface is needed, put IIC\_EN to VDD, not to ground. You must not leave this pin open.

Once programmed, the device can operate stand-alone. As both interfaces are limited to slave rank, stand-alone operation with data transfer to an ancillary device (e.g. an LCD converter or a D/A converter) will necessitate software implementation of a serial protocol (contact ACAM for details).

### 4.1.1 Op codes

Table 4-1: 8-Bit Op Code Commands

| 'h88 | Power-up reset. This command resets everything.                                     |

|------|-------------------------------------------------------------------------------------|

| 'h8A | "Initial" or "partial" reset, leaves the SRAM contents and registers unchanged. Re- |

|      | sets important parts of the device like the front-end and DSP                       |

| 'h8C | Start a capacitance measurement sequence                                            |

| 'h84 | Terminate the write-to-OTP process                                                  |

| 'h8E | Start temperature measurement                                                       |

### Table 4-2: 24-Bit Op Code Commands

| Command       | Ву | te 2 | 2 |    | Byte 1       | Byte O   |

|---------------|----|------|---|----|--------------|----------|

| Write to SRAM | 1  | 0    | 0 | 1  | Address<11O> | Data<70> |

| Read SRAM     | 0  | 0    | 0 | 1  | Address<11O> | Data<70> |

| Write to OTP  | 1  | 0    | 1 | Ac | ddress<12O>  | Data<70> |

| Read OTP      | 0  | 0    | 1 | Ac | ddress<12O>  | Data<70> |

### Table 4-3: 32-Bit Op Code Commands

| Command      | Byte | 3 |                | Byte 2             | Byte 1                               | Byte O |  |  |

|--------------|------|---|----------------|--------------------|--------------------------------------|--------|--|--|

| Write Config | 1    | 1 | Cf_Address<50> | Registry Param     | eter<230>                            |        |  |  |

| Read Results | 0    | 1 | Rs_Address<50> | Measurement F      | Measurement Results<230> or Measure- |        |  |  |

|              |      |   |                | ment Results<4724> |                                      |        |  |  |

For Cf\_Address, see section 5.1 below, and for Rs\_Address, section 5.3 below.

# 4 Interfaces (Serial And Pulse-Density)

### 4.1.2 I<sup>2</sup>C Compatible Interface

The present paragraph outlines the PCapO1 device specific use of the I<sup>2</sup>C interface. For a general description of ACAM's subset of the I<sup>2</sup>C interface see the dedicated data sheet. See also the PCapO1 bug report at the end of the present sheet.

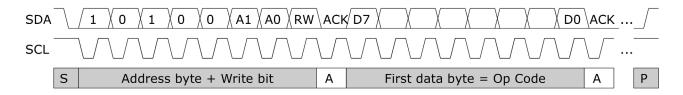

The external master (PCap cannot be master) begins the communication by sending a start condition, falling edge on the SDA line while SCL is HIGH. It stops the communication by a stop condition, a rising edge on the SDA line while SCK is high. Data bits are transferred with the rising edge of SCK.

On I<sup>2</sup>C buses, every slave holds an individual 7-bit device address, The address always has to be sent as the first byte after the start condition, the last bit indicating the direction of the following data transfer.

Address byte:

| MSB |   |       |      |      |    |    | LSB |

|-----|---|-------|------|------|----|----|-----|

| 1   | 0 | 1     | Ο    | 0    | A1 | AO | R/W |

|     |   | fixed | vari | able |    |    |     |

Default address: A1 = A0 = 0

The address byte is followed by the opcode and eventually the payload. Each byte is followed by an acknowledge bit (= 0). PCapO1 has 8-bit, 24-bit and 32-bit opcodes, listed in tables 4-1 to 4-3. Figure 4-1: I<sup>2</sup>C principle sequence

### I<sup>2</sup>C Write

During write transactions, the master alone sends data, the addressed slave just sends the acknowledge bits. The master first sends the slave address plus the write bit. Then it sends the PCap specific opcode including the register address in the slave. Finally it sends the payload ("Data"). Figure 4-2 I<sup>2</sup>C Write, an example

|   |                     |   |          |   |                 |   |       |   | • |

|---|---------------------|---|----------|---|-----------------|---|-------|---|---|

| S | S I2C-Address + W A |   | A Opcode |   | A Write address |   | Data  | А | Ρ |

|   |                     |   |          |   |                 |   |       |   |   |

| S | 1010000 0           | 0 | 'h 90    | 0 | 'h 47           | 0 | 'h FF | 0 | Ρ |

"Write RAM"

# 4 Interfaces (Serial And Pulse-Density)

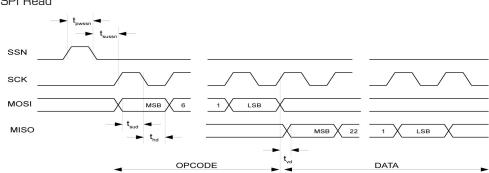

### I<sup>2</sup>C Read

During read transactions, the direction of communication has to be commuted. Therefore, the master sends again a start condition plus the slave address plus the **read bit** (instead of the write bit) to switch into read mode. Figure 4-3 shows an example with opcode "read RAM". The master sets a Not-Acknowledge (1) to indicate "end read", "stop sending" to the slave.

Figure 4-3: I<sup>2</sup>C Read

|   |                 |   |        |   |              |   | _^ |                 |   |       |   |   |

|---|-----------------|---|--------|---|--------------|---|----|-----------------|---|-------|---|---|

| S | I2C-Address + W | А | Opcode | А | Read address | А | S  | I2C-Address + R | А | Data  | Ν | Ρ |

| S | 1010000 0       | 0 | 'h 10  | 0 | 'h 47        | 0 | S  | 1010000 1       | 0 | 'h FF | 1 | Р |

"Read RAM"

### 4.1.3 The 4-wire, SPI interface

Clock Polarity, Clock Phase and Bit Order. The following choices are necessary for successful operation.

| SPI - Parameter | Description        | Setting      |

|-----------------|--------------------|--------------|

| CPOL            | Clock polarity     | 0            |

| CPHA            | Clock phase        | 1            |

| Mode            | SPI Mode           | 1            |

| DORD            | Bit sequence order | O, MSB first |

Table 4-4: SPI Clock Polarity, Clock Phase and Bit Order

Timing conditions:

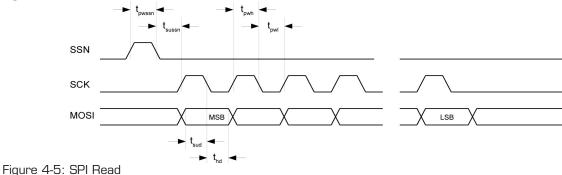

Figure 4-4: SPI Write

# 4 Interfaces (Serial And Pulse-Density)

Table 4-5: SPI timing parameters

| Name                                | Symbol   | VDD=2.2 V | VDD=3.0 V | VDD=3.6 V | Units |

|-------------------------------------|----------|-----------|-----------|-----------|-------|

| Serial clock frequency              | fSPI-bus | 10        | 17        | 20        | MHz   |

| Serial clock pulse width HI state   | tpwh     | 50        | 30        | 25        | ns    |

| Serial clock pulse width LO state   | tpwl     | 50        | 30        | 25        | ns    |

| SSN enable-to-valid latch           | tsussn   | 10        | 8         | 7         | ns    |

| SSN pulse width between write       | tpwssn   | 50        | 30        | 25        | ns    |

| cycles                              |          |           |           |           |       |

| Data setup time prior to clock edge | tsud     | 7         | 6         | 5         | ns    |

| Data hold time after clock edge     | thd      | 5         | 4         | 3         | ns    |

| Data valid after clock edge         | tvd      | 40        | 26        | 16        | ns    |

## 4.2 PDM/PWM and GPIO

### Pulse-Density / Pulse Width Code Interfaces and General-Purpose Ports

The following table shows the different general purpose ports and their possible assignment.

| External Port Name | Description        | Direction in or out |  |  |

|--------------------|--------------------|---------------------|--|--|

| PGO                | SSN (in SPI-Mode)  | in                  |  |  |

|                    | DSPØ or DSP2       | in(1) / out         |  |  |

|                    | FFO or FF2         | in(1)               |  |  |

|                    | PulseO             | out                 |  |  |

| PG1                | MISO (in SPI-Mode) | out                 |  |  |

|                    | DSP1 or DSP3       | in(1) / out         |  |  |

|                    | FF1 or FF3         | in(1)               |  |  |

|                    | Pulse1             | out                 |  |  |

| PG2                | DSPØ or DSP2       | in(1) / out         |  |  |

|                    | FFO or FF2         | in(1)               |  |  |

|                    | PulseO             | out                 |  |  |

|                    | INTN               | out                 |  |  |

| PG3                | DSP1 or DSP3       | in(1) / out         |  |  |

|                    | FF1 or FF3         | in(1)               |  |  |

|                    | Pulse1             | out                 |  |  |

| PG4                | DSP4 (output only) | out                 |  |  |

| PG5                | DSP5 (output only) | out                 |  |  |

Table 4-6: General-Purpose Port Assignment:

(1) These ports provide an optional debouncing filter and an optional pull-up resistor.

# 4 Interfaces (Serial And Pulse-Density)

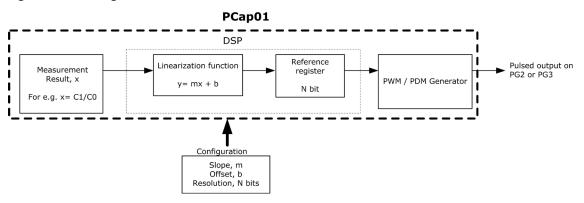

There is a possibility to generate pulse width or pulse density code as outputs from the chip, based on the measurement results and using standard firmware (or some other, possibly derived from Standard). Any of the capacitance or temperature measurement results can be used to generate the pulsed output, and the selection is made by setting the pulse1\_select (resp. pulseO\_select) in register Param2. The pulse codes may be output through general-purpose ports PGØ and PG1 (or two others). Destination ports are to be configured **as output** using the PG DIR IN bits in Register 9.

As one can see from above, ports PGØ and PG1 are seemingly not available for pulse output when assigned to the SPI interface. In most cases, though, where pulse outputs are wanted, SPI interface is used for programming only. Hence, after programming, the programmer is removed, pin/pad VPP\_OTP is set LOVV, and pin/pad IIC\_EN is set HIGH. Once this is done, all PG ports are available for general-purpose use and especially PGO, PG1 for the pulses.

The pulse-modulated output signal can be transformed into an analog voltage through a Low Pass filter. The Pulse Width Modulated output needs a low pass filter of higher order, while for Pulse Density Modulated signal a simple LP filter is sufficient. Suggested dimensioning is 220 kOhm / 100 nF, which smoothes the ripple to less than 1 LSB.

For generating the pulsed outputs, the frequency of the carrier clock signal is configurable to either 8 MHz or 1 MHz or 100 kHz. However, for best results, the "OLF\_X2" 100 kHz clock is recommended. It can be selected

Figure 4-6: PDM Output filtering

through PI1\_CLK\_SEL (resp. PIO\_CLK\_SEL) in Register 9. The resolution of the Pulse interface has to be configured through PI1\_RES (resp. PIO\_RES) in Register 9. The result of measurement from capacitance or temperature is a 24-bit value. The DSP linearizes this 24 bit result to a 10 bit value (assuming "10 bit resolution" setting). The parameters Slope (m) and Offset (b) of the linear function are configurable in Registers Param3 to Param5. Both, offset and slope can be set to either positive or negative values. The setting of the slope and offset limits the range of the output signal and hence determines the voltage range of the filtered analog signal. A 10-bit resolution thus limits the result

# 4 Interfaces (Serial And Pulse-Density)

value between O and 1023. For lower-bit resolutions, the range reduces accordingly. The following figure depicts how the result is processed to generate the pulsed output. Figure 4-7: Pulse generation

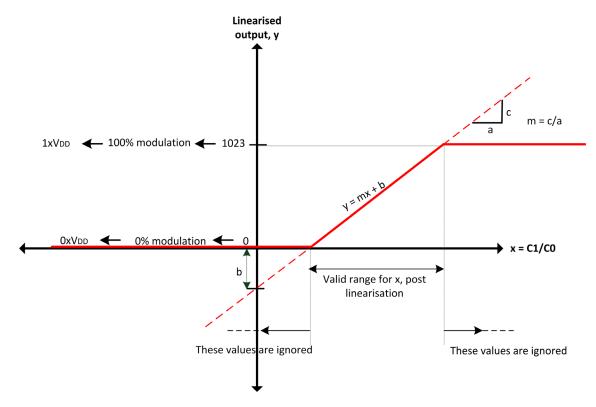

The following figure shows a sample linear function and its parameters graphically. In this graph, the result C1/CO has been taken on the x-axis, assuming that this result is to be pulse modulated. Here the value of m is positive and b is negative. 10 bit resolution has been configured.

Figure 4-8: PWM-PDM linearisation

# 4 Interfaces (Serial And Pulse-Density)

By setting the value of m and b, the linearization function limits the range of the output x as shown. Values outside these limits are ignored. Thereby knowing the range in which the results might change, the parameters of the linearization function can be fed accordingly. The lower limit of the valid range corresponds to 0% modulation (all bits are 0), this is the least possible value of the output (O). The upper limit of the valid range corresponds to 100% modulation (all bits are 1), and this is the maximum possible value of output. 10 bit resolution implies that this maximum value is 1023. For lower bit resolutions, this maximum value will come down accordingly. In terms of voltage, the two limits correspond to OV and Vdd.

#### Applications:

- A typical case would be outputting capacitance result through PGO and temperature result through PG1. Calculation and copying to the output registers must be performed by firmware. See help windows in the dedicated PCapO1 assembler code editor.

- Useful for applications for which reading the results out through the SPI/ I2C interface is not suitable because of speed limitations or applications requiring an analog output signal.

- A temperature-coded pulse stream could be low-pass filtered and then directly used for temperature control.

Please note that the entire linearization task as described here is performed by firmware, especially the standard firmware.

| 5     | Wri   | ite & Read Registers                        | 5-2  |

|-------|-------|---------------------------------------------|------|

| 5.1   | Confi | guration & Parameter Registers              | .5-2 |

| 5.2   | Expla | nations to Configuration Registers          | 5-12 |

| 5.2.1 | I     | Comments on Register 0                      | 5-12 |

| 5.2.2 | 2     | Comments on Register 2                      | 5-13 |

| 5.2.3 | 3     | Comments on Register 3                      | 5-13 |

| 5.2.4 | Ļ     | Comments on Registers 3 an 4 (timing rules) | 5-13 |

| 5.2.5 | 5     | Comments on Registers 4 and 5               | 5-14 |

| 5.2.6 | 5     | Comments on Register 6                      | 5-14 |

| 5.2.7 | ,     | Comments on Register 8                      | 5-15 |

| 5.2.8 | 3     | Comments on Register 9                      | 5-15 |

| 5.3   | Read  | Registers                                   | 5-16 |

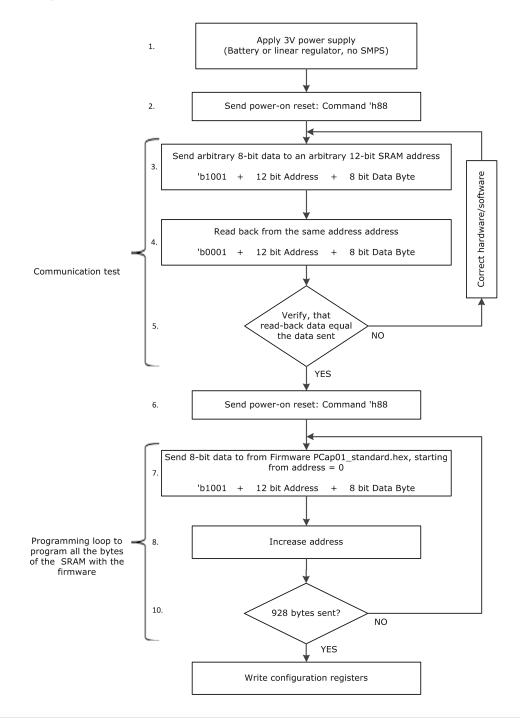

The PCapO1Ax-VO3O1 with the standard firmware O3.O1.xx offers 21 configuration and parameter registers and 13 read registers. The configuration registers cannot be read back. So, for communication test use the "Write to SRAM" & "Read SRAM" opcodes.

The configuration registers (address 0 through 10) directly set the hardware like CDC, RDC, interfaces, clocks and DSP. The parameter registers (address 11 through 19) set values in the firmware and therefore are firmware specific.

### 5.1 Configuration & Parameter Registers

Overview:

| Address | Name        | Description                                                                                                                                                        | Target   |

|---------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 0       | Register O  | OTP settings: MEMCOMP, ECC_MODE, AUTOBOOT_DIS, MEM_LOCK_DIS                                                                                                        | Hardware |

| 1       | Register 1  | Fixed default                                                                                                                                                      | Hardware |

| 2       | Register 2  | C-measurement settings: CMESS_PORT_EN, CMEAS_BITS, RDCHG_INT_SEL                                                                                                   | Hardware |

| 3       | Register 3  | C-measurement settings: CY_CLK_SEL, SEQ_TIME, CMEAS_FAKE, C_AVRG                                                                                                   | Hardware |

| 4       | Register 4  | C/T-measurement settings: CMEAS_STARTPIN, CMEAS_TRIG_SEL,<br>CMEAS_CYTIME, TMEAS_CYTIME, TMEAS_STARTPIN, TMEAS_TRIG_SEL                                            | Hardware |

| 5       | Register 5  | T-measurement settings: T_AVRG, TMEAS_TRIG_PREDIV                                                                                                                  | Hardware |

| 6       | Register 6  | T-measurement settings: TMEAS_FAKE, TMEAS_7BITS                                                                                                                    | Hardware |

| 7       | Register 7  | Fixed default                                                                                                                                                      | Hardware |

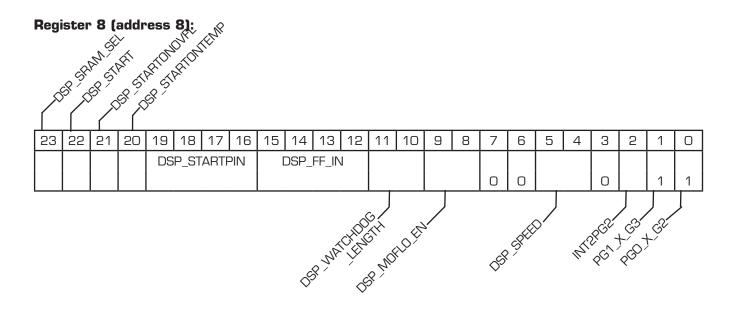

| 8       | Register 8  | DSP configuration : DSP_SRAM_SEL, DSP_START, DSPSTARTONOVL,<br>DSP_STARTONTEMP, DSP_STARTPIN, DSP_FF_IN, DSP_WATCHDOG_<br>LENGTH, DSP_MOFLO_EN, DSP_SPEED, INT2PG2 | Hardware |

| 9       | Register 9  | GPIO settings: PG_DIR_IN, PG_PULL_UP, PI_EN, PI1_CLK_SEL, PI0_CLK_SEL, PI1_RES, PI0_RES                                                                            | Hardware |

| 10      | Register 10 | Control of internal 1.8 V regulator                                                                                                                                | Hardware |

| 11      | ParamO      | Not used                                                                                                                                                           | Firmware |

| 12      | Param1      | Not used                                                                                                                                                           | Firmware |

| 13      | Param2      | Pulsed output setting: pulse_select                                                                                                                                | Firmware |

| 14      | Param3      | Pulsed output setting: pulseO_slope                                                                                                                                | Firmware |

| 15      | Param4      | Pulsed output setting: pulseO_offset                                                                                                                               | Firmware |

| 16      | Param5      | Pulsed output setting: pulse1_slope                                                                                                                                | Firmware |

| 17      | Param6      | Pulsed output setting: pulse1_offset                                                                                                                               | Firmware |

| 18      | Param7      | C-measurement setting: differential                                                                                                                                | Firmware |

| 19      | Param8      | Gain_Corr                                                                                                                                                          | Firmware |

| 20      | Register 20 | RUNBIT                                                                                                                                                             | Hardware |

#### Register Description in Detail:

| Bit number $ ightarrow$          | 15 | 14 | 13   | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------------------------|----|----|------|----|----|----|---|---|---|---|---|---|---|---|---|---|

| parameter $ ightarrow$           |    |    | para | m1 |    |    |   |   |   |   |   |   |   |   |   |   |

| Recommended value $  ightarrow $ |    |    |      |    |    |    | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 |

#### Register O (address O):

| 23 | 22 | 21 | 20   | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12    | 11   | 10 | 9 | 8 | 7  | 6   | 5     | 4   | З  | 2   | 1    | 0   |

|----|----|----|------|----|----|----|----|----|----|----|-------|------|----|---|---|----|-----|-------|-----|----|-----|------|-----|

|    |    |    |      |    |    |    |    |    |    | E  | ECC_I | MODI | Ξ  |   |   | AL | TOB | DOT_I | DIS | ME | M_L | JCK_ | DIS |

| 0  | 1  | 0  | 0    |    |    | 1  | 0  |    |    |    |       |      |    |   |   |    |     |       |     |    |     |      |     |

|    |    | 7  | EMCO | MP |    |    |    |    |    |    |       |      |    |   |   |    |     |       |     |    |     |      |     |

| Parameter    | Description                                                      | Settings                                                                                                                                                   |

|--------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MEMCOMP      | Bits 18 and 19 control the SRAM-to-OTP-<br>comparison mechanism. | 0 = disable<br>1 = 5 Byte<br>2 = 33 Byte<br>3 = 257 Byte                                                                                                   |

| ECC_MODE     | OTP-internal error detection and repair me-<br>chanism.          | OxOO = Disabled ("single"); limit=4032 Byte<br>OxOF = "Double" mode; limit=4032 Byte<br>OxFO = "Quad" mode; limit=1984 Byte                                |

| AUTOBOOT_DIS | Automatic self boot from OTP                                     | OxO = stand-alone operation and the device then boots automatically from OTP.                                                                              |

|              |                                                                  | OxF = slave operation and the device is interface booted.                                                                                                  |

| MEM_LOCK_DIS |                                                                  | OxO = activating the memory read-out blo-<br>cker, which helps preventing the firmware<br>from being read and thus protects your<br>intellectual property. |

|              |                                                                  | OxF = Readout remains un-blocked                                                                                                                           |

BYTE O (bits 7...O) cannot be written directly through the interface, but can only be copied from the OTP. This is part of the memory-secrecy mechanism protecting the OTP against reverse-engineering disassembly attempts.

#### Register 1 (address 1):

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| Ο  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0 | Ο | 0 | Ο | 1 | Ο | Ο | Ο | 1 | Ο |

# **PICO**CAP

| 5 Write<br>Register 2 (address | & Read Registers                                                                                                   | A DE DE                                                      |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| 23 22 21 20 15                 | ) 18 17 16 15 14 13 12 11 10                                                                                       | 9 8 7 6 5 4 3 2 1 0                                          |

| CMEAS_POF                      |                                                                                                                    |                                                              |

|                                | C GRO FLIAT                                                                                                        |                                                              |

| Parameter                      | Description                                                                                                        | Settings                                                     |

| CMEAS_PORT_EN                  | CDC port mask                                                                                                      | Bit 16 enables port PCO, bit 17 enables<br>PC1 and so forth. |

| C_GRD_FLOAT                    | Sensor connecting scheme. See section                                                                              | b'OO = grounded single capacitances                          |

|                                | 3.4                                                                                                                | b'00 = grounded differential caps (same)                     |

|                                |                                                                                                                    | b'O1 = floating single capacitances                          |

|                                | Coloction of minner symmetric charge and                                                                           | b'10 = floating differential capacitances                    |

| CMEAS_DUMMY_EN                 | Selection of mirror symmetric charge and<br>discharge for differential capacitors, avoi-<br>ding mechanical stress | 1 = activated                                                |

| COMPENS_EXT_DIS                | Turn off compensation measurement for                                                                              | O = external compensation activated                          |

|                                | external parasitic capacitances                                                                                    | 1 = external compensation disabled                           |

| COMPENS_INT_DIS                | Turn off compensation measurement for internal parasitic capacitances                                              | O = internal compensation activated                          |